Intel® OFS support

SmartNIC powered by Agilex™ FPGA

N6060

N6060

Smart Network Interface Card (NIC) for COTS server PCIe slots, based on the Intel® Agilex™ FPGA SmartNIC N6000 platform, with incorporated support for Intel Open FPGA Stack (OFS).

Intel, the Intel logo, and other associated names and logos are trademarks of Intel Corporation or its subsidiaries.

Features

SmartNIC for COTS server PCI-Express slots

The Griffin-N6060 form factor is PCI-Express x16 (x2 x8 bifurcation).

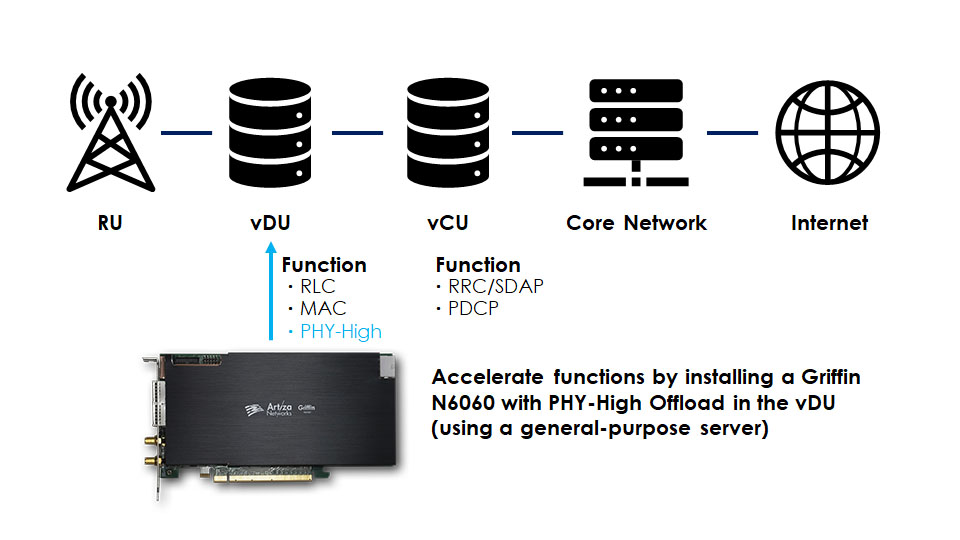

Offload and accelerate vRAN/O-RAN functions built on COTS servers.

Contribute to cost reductions for vRAN/O-RAN.

Intel® OFS (IOFS) Support

Griffin-N6060 supports Intel® OFS and can be used for a wide variety of applications.

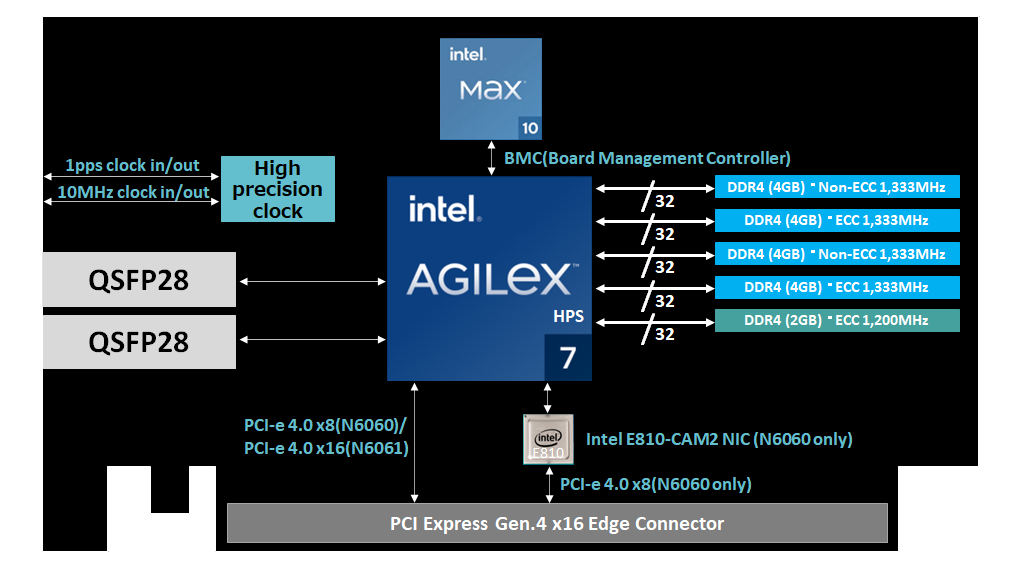

The on-board FPGA, Intel® Agilex™ 7 F Series AGFB027, boasts ample resources and an expansive user area (AFU).

Cortex®-A53 CPU + 2GB DDR4 SDRAM

Built in to the Intel® Agilex™ 7 F series is the Arm® Cortex®-A53 quad-core CPU.

Dedicated 2GB DDR4 memory and a dedicated storage SD card slot enable implementation of PTP/SyncE for time synchronization, etc.

Built-in BMC

An Intel® MAX® 10 CPLD is installed as the Board Management Controller (BMC).

The BMC can drive various IOFS-supported functions, including power/temperature management, reset control, and FPGA configuration.

Specifications *current to January 2023

| Name | Griffin N6060/N6061 |

|---|---|

| FPGA | Intel® Agilex™ 7 AGFB027R25A2I2V |

| Ethernet I/F | 100GbE x2 /25GbE x2 x2/10GbE x8 |

| Form Factor | PCI Express Gen.4 x2 x8 Bifurcation (N6060) / x16 (N6061) |

| RAM | 16GB DDR4 (FPGA Fabric) + 2GB DDR4 (For CPU with built-in FPGA) |

| Network Interface Chip | Intel® E810-CAM2 |

| Card Size | Full Height 3/4 Length |

| Power | Bus power: max 75W + 4x2 pin connector max: 150W (cannot be operated with only bus power) |

| Board Management Chip | Intel® MAX® 10 |

| Time Synchronization | PTP/SyncE support, 1PPS in/out SMA connector |

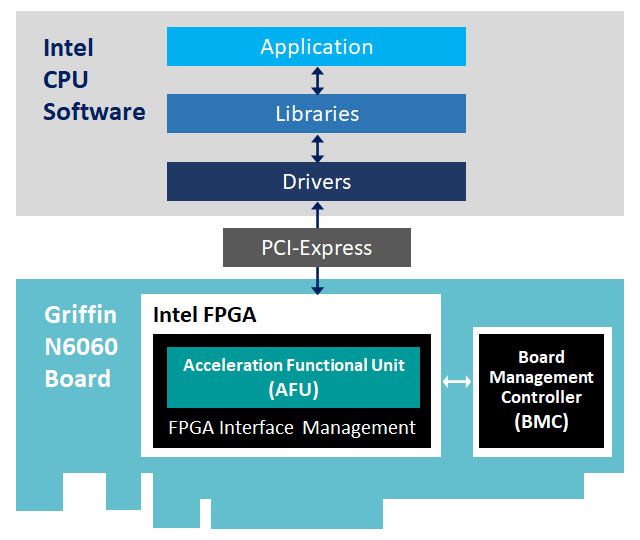

Griffin-N6060/N6061 block diagram

SmartNIC Use Case: vRAN

About Intel® OFS

Intel® OFS (Open FPGA Stack) is a platform that packages libraries, drivers, and RTL to run applications.

Software

- Application layer

- OPAE (Open Programmable Acceleration Engine) libraries, tools and APIs

- Upstreamed, open source kernel drivers

Hardware

- FPGA Interface Manager (FIM)

- Acceleration Function Unit (AFU) area for workload development using sample AFUs *

- Boad Management Controller(BMC)

*RTLs developed by the customer will be embeddd in the AFU area.